## Through Silicon Vias cleaning for quantum computer interconnects integration

Harold LE TULZO<sup>1</sup>, Loriana CELESTE<sup>1</sup>, Jaber DERAKHSHANDEH<sup>2</sup>, Carine GERETS<sup>2</sup>, Jean CHARBONNIER<sup>3</sup>, Candice THOMAS<sup>3</sup>, Edouard DESCHASEAUX<sup>3</sup>, Jérôme DAVIOT<sup>1</sup>

<sup>1</sup> Technic France, 15 rue de la Montjoie, BP 79, 93212 Saint-Denis La Plaine, France <sup>2</sup> IMEC, Kapeldreef 75, 3001 Leuven, Belgium <sup>3</sup> CEA-LETI, Univ. Grenoble Alpes, F-38000 Grenoble, France

Quantum computing based on superconducting Josephson junction qubits is an attractive technology path for performing ultra-fast and efficient calculations. The MATQu (**MAT**erials for **Qu**antum Computing) project aims at developing state-of-the-art qubits and is supported by European academic partners, leading Research Technology Organisations (RTO's), and participants in the semiconductor value chain including equipment and chemical suppliers as well as end-users.

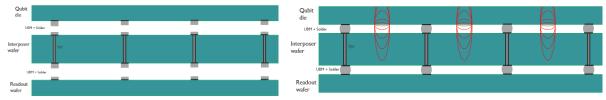

Technic France, owing to its expertise in electroplating and surface preparation (stripping, etching, cleaning) has been challenged within the "3D integration and packaging" workflow alongside expert teams from IMEC and CEA Leti. The common goal is to develop and validate a novel interposer design to interconnect in a 3D multi-stacking manner, qubits with readout wafer (see Figure 1) [1].

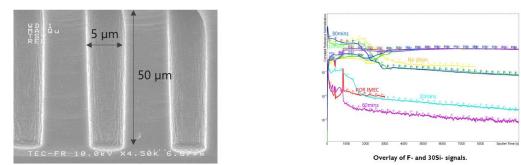

New materials stacks [2] that are compatible for cryogenic conditions must be integrated for under bump metallization (UBM), solder bumps [3] and through-silicon vias (TSV's). The design of 5 µm diameter TSV with high-quality material bottom-up plating will require efficient surface preparation and complete removal of chemically resilient post etch residues. In the frame of the MATQu project, IMEC and CEA Leti have been focused upon TSV etching and wafer patterning, while Technic France has been focused on TSV cleaning.

Figure 1 – Solder bumps and TSV formation in interposer wafer for qubit and readout wafers interconnection, before (left) and after (right) bonding.

Following standard Bosch dry etch, high aspect ratio TSV sidewalls are covered with thick inert fluoropolymer, which is detrimental and can cause, among other issues, barrier layer delamination, and an increased thermal stress due to poor fluoropolymer conformality. For quantum applications, this could create loss mechanisms that can damage the coherence and Q factor of qubits, thus reducing device yield [4;5]. Complete removal of these fluoropolymer residues is therefore mandatory.

Current processes of record are either dry (O<sub>2</sub> ashing) or wet [6;7]. Among the wet cleaning solutions, to our best knowledge, none are capable of complete sidewall fluoropolymer and photoresist removal while i) remaining chemically compatible with exposed materials,

especially metals; ii) maintaining a long effective bath life; and iii) avoiding the use of chemical components that are not bioaccumulative nor CMR-listed.

Against these requirements, we have developed TechniClean BOS-347, which has been extensively investigated with partners over several structures patterned by using a standard Bosch dry etch. A comprehensive data set including SEM images, thin-film metrology, and surface analyses such as ToF-SIMS validating post-Bosch etch cleaning efficiency and benchmarking new versus legacy cleaning candidates (wet and ash/wet) will be presented (see Figure 2).

Figure 2 – TSV etched in the frame of the MATQu project by IMEC (left) and ToF-SIMS analyses of the middle parts of the TSV comparing various solutions and processes.

*This project leading to this application has received funding from the ECSEL Joint Undertaking (JU) under grant agreement No* <u>101007322</u>. *The JU receives support from the European Union's Horizon 2020 research and innovation program and Germany, France, Belgium, Austria, Netherlands, Finland, Israel.* (Please visit the project website <u>www.matqu.eu</u> for more information).

[1] D.R.W. Yost and al., « Solid-state qubits integrated with superconducting through-silicon vias ». npj Quantum Information, vol. 6, n° 1, pp. 59, December 2020.

[2] C. Gerets and al., « Process development and characterization of 3D multi-die stacking », in IEEE 8th Electronics System-Integration Technology Conference (ESTC), September 2020, pp. 1-6.

[3] C. Thomas and al., « Electrical and Morphological Characterizations of 3-D Interconnections for Quantum Computation », in IEEE Transactions on Components, Packaging and Manufacturing Technology, vol. 12, n° 3, pp. 462-468, March 2022.

[4] J. Kraft and al., « Passivation integrity investigations for through wafer interconnects », in IEEE International Reliability Physics Symposium, Phoenix, AZ, USA, April 2008, pp. 506–509.

[5] K. Grigoras and al., « Qubit-compatible substrates with superconducting through-silicon vias », arXiv, pp. 7, January 2022.

[6] A. Hryciw, « Bosch polymer removal comparison », University of Alberta – nanoFAB on May 13, 2020. https://www.nanofab.ualberta.ca/2020/news/bosch-polymer-removal-comparison/

[7] P. G. Clark and al., « The use of segregated hydrofluoroethers as cleaning agents in electronics packaging applications », in International Conference on Soldering and Reliability, Toronto, Ontario, CANADA, May 2009.